RISC-V Systems Lab

Welcome to the RISC-V Systems Lab

India’s frontier lab for open-source hardware innovation. At the intersection of semiconductors, systems architecture, and AI acceleration, we’re crafting the next generation of energy-efficient, high-performance processors and system-on-chip (SoC) designs powered by the revolutionary RISC-V instruction set architecture.

Our mission is foundational: to build India’s sovereign semiconductor ecosystem from the ground up — one chip, one board, one instruction at a time.

From AI-optimized edge devices to custom-designed silicon for healthcare, robotics, and scientific computing, this is where ideas become circuits, and students become silicon architects.

For Students

Become a Chip-to-System Engineer

Want to go deeper than code and actually design the machines that run it? At the RISC-V Systems Lab, you’ll work at the bleeding edge of hardware engineering — from digital logic design to full-stack system architecture. You won’t just learn about semiconductors — you’ll build them.

What We Offer:

01

A Trailblazing Three-Year Program

Our intensive program is divided into six six-month stages. Students learn through build-first exploration — progressing from logic gates to complete systems and chip deployments, guided by India’s top semiconductor educators and industry mentors.

02

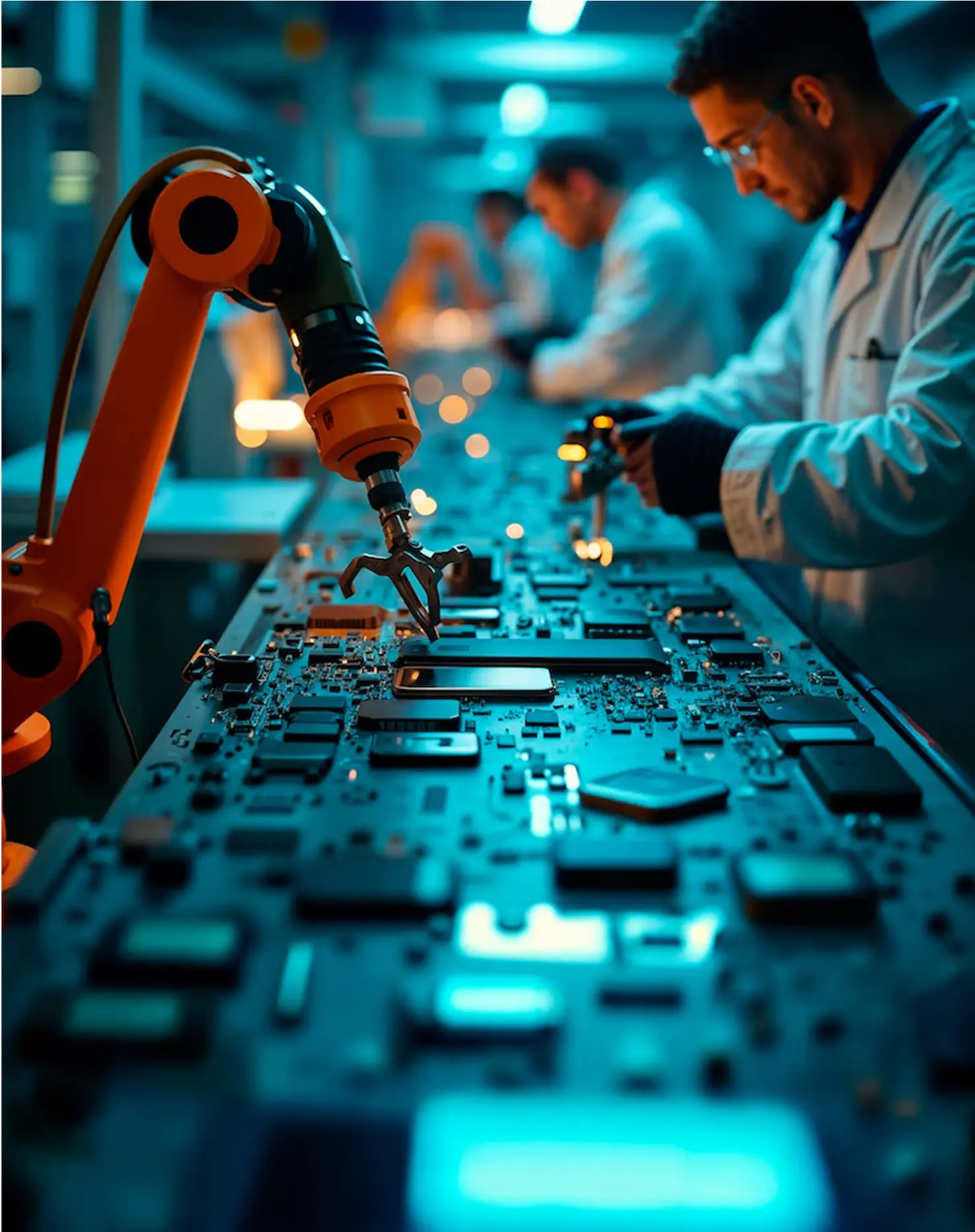

Real Industry Hardware Projects

Collaborate with Indian semiconductor fabs, RISC-V International members, and AI hardware startups. Build AI inference chips, sensor integration boards, and custom embedded systems for robotics, vision, and healthcare.

03

A Culture of Hardcore Hardware Innovation

Welcome to a lab of oscilloscopes, FPGAs, and late-night schematics. Here, software meets silicon. You’ll prototype, simulate, fabricate, and optimize real working systems — hands-on, every day.

04

An Open-Source Silicon Stack

You’ll master open tools that power the world’s next chips:

A Three-Year Journey

From Logic to Launch

Level 1

Remembering

Learn the fundamentals of digital logic, binary systems, processor architecture, and RISC-V basics.

Level 2

Understanding

Understand how instructions are decoded, how data flows inside chips, and how architecture affects performance.

Level 3

Applying

Design and simulate RISC-V cores, program FPGAs, and integrate peripherals in real-world projects.

Level 4

Analyzing

Evaluate chip designs, analyze bottlenecks, compare instruction sets, and optimize system efficiency.

Level 5

Evaluating

Benchmark custom designs, test performance under real loads, and validate silicon for reliability.

Level 6

Creating

Design your own SoC or AI accelerator — taped out or deployed on FPGAs — solving real-world problems with home-grown silicon.

Our Collaborative Ecosystem The Hardware-Software Nexus

The RISC-V Systems Lab operates in symphony with other forward-looking labs to bring hardware innovation to life:

Foundation Model Lab

Integrate with foundation models to co-design AI-optimized chips for speed, power, and performance.

Soft Brain Lab

Power intelligent software agents at the edge with custom embedded compute engines.

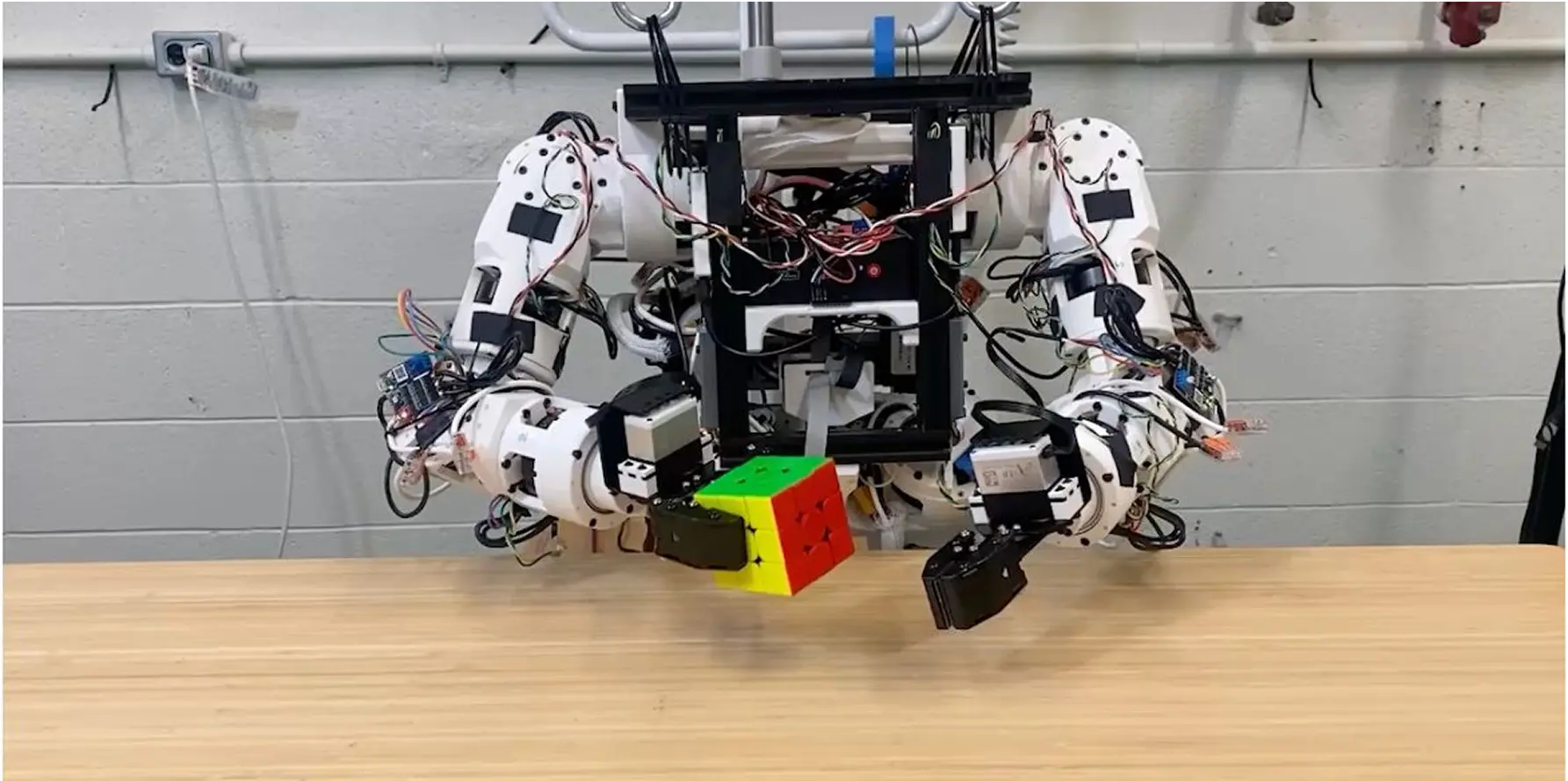

Embodied AI Brain Lab

Build controllers and processors for surgical robots, drones, and AI-powered physical systems.

Augmented Human Lab

Design ultra-efficient hardware pipelines for AR/VR and next-gen holographic interfaces.

This interdisciplinary network makes you more than a roboticist — it turns you into a hybrid thinker, a systems builder, and a leader in embodied intelligence.

Join Us

Build Chips That Build the Future

The RISC-V Systems Lab is more than an academic lab — it’s the birthplace of India’s next generation of chip designers and hardware system engineers. If you’re passionate about silicon, architecture, and making technology faster, smaller, and smarter — this is your battleground.

NAAC A+

NIRF Ranked 101-150

AESTR Ltd © 2025